IoTで機器の成りすましを防止、「ICの指紋」技術を低コストで実現(産業技術総合研究所)

産業技術総合研究所(産総研・ナノエレクトロニクス研究部門)は7日、半導体ICチップの偽造を防ぐ「ICの指紋」を、低コスト・高信頼性・コンパクトに実現できる素子とそれを用いた回路技術を新たに開発したことを発表した。

製品・サービス・業界動向

業界動向

「ICの指紋」技術とは、ICチップ作製時に自然に発生する“ばらつき”を利用し、チップに固有の番号を発生させる技術のこと。この番号を秘密鍵として認証に用いれば、不正なリサイクルチップや偽造チップによる事故や不正アクセスを防止できる。

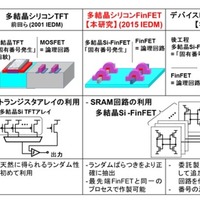

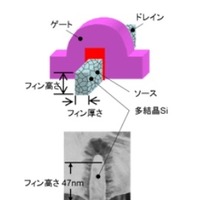

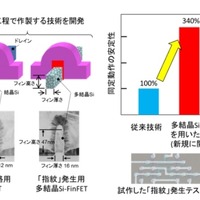

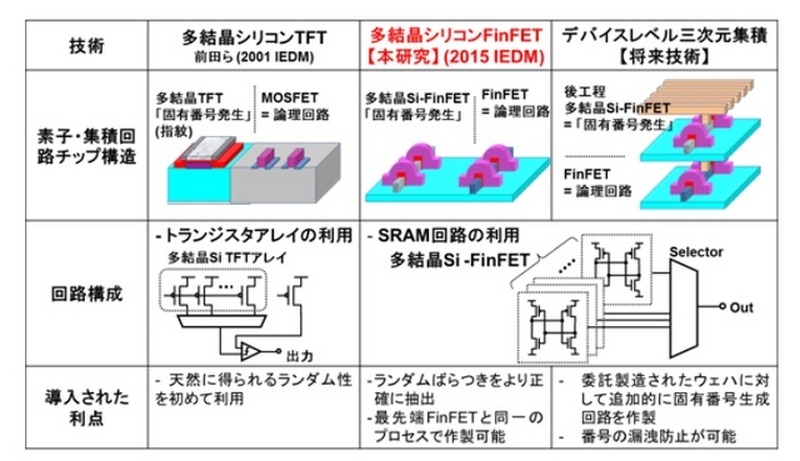

多結晶シリコン素子による「ICの指紋」技術は2001年に初めて提唱されたが、通常型トランジスタと異なる構造のため、製造工程が複雑になる問題があった。産総研では、多結晶シリコン素子技術に長く取り組んでおり、今回、多結晶シリコンの「FinFET」(MOS構造を用いた電界効果型トランジスタ)を用いて「ICの指紋」を発生させる回路を、チップ内に形成する技術を開発した。

これにより、通常のIC用トランジスタを用いた場合に比べ、3倍以上の動作安定性で固有番号を発生できるとのこと。製造も低コストに行えるため、将来的に、IoTなどで機器の成りすましを防止する技術として期待される。

半導体チップの偽造を防ぐ「ICの指紋」、産総研が低コスト化に成功

《冨岡晶@RBB TODAY》

関連記事

-

その技術なら、マレーシア航空 370 便を ID 詐欺から防ぐことができた~キーパッドセキュリティ搭載? 彼らは決して実現しなかっただろう(The Register)

国際 -

銀行が手のひら認証キットを振りかざす――それは切断された手に反応しない~アイデンティティ詐欺と戦うための新たな決済システムとは(The Register)

国際 -

ブラウザメーカー各社が、偽の Google.com セキュリティ証明書のブロックに大あわて~トルコの権威によるヘマが、データを危険にさらすかもしれない(The Register)

国際 -

真贋判定用UHFラベルを用いて偽造品対策(凸版印刷)

製品・サービス・業界動向

この記事の写真

/