PRISMにおける不正ハードウェアチップ検知手法の研究開発に採択(ラックほか)

ラックは、総務省が2019年度に実施する内閣府事業PRISMの対象研究開発課題「設計・製造におけるチップの脆弱性検知手法の研究開発」の委託先として、学校法人早稲田大学を代表研究機関とし、株式会社KDDI総合研究所およびラックが選定されたと発表した。

製品・サービス・業界動向

業界動向

電子機器が急増し、新たな価値やサービスが次々に創出され人々に豊かさをもたらす一方で、複雑化するサプライチェーン全体のセキュリティ確保が重要な課題となっている。特に、電子機器のハードウェア上に組み込まれた不正なチップは製品出荷後に交換・修正することが難しく、その影響は極めて深刻になる可能性があることから、設計・製造におけるチップの脆弱性検知手法の確立は急務とされている。

そこで、2つの課題とそれらに対する研究開発を行うこととなった。課題と研究開発は次の通り。この研究により、サプライチェーン運用技術の確立と、国際競争力の強化を目指す。

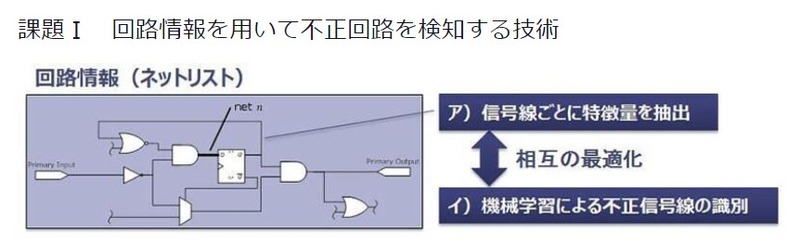

課題 I:回路情報を用いて不正回路を検知する技術

(ア)不正回路について、その種類及び機能を明確化したうえで、不正回路と不正でない回路とを識別するための特徴量を抽出する技術の研究開発。

(イ)AIを活用し不正回路の特徴量と不正でない回路の特徴量を学習することにより、不正回路の有無及び不正回路の存在する位置を検知する技術の研究開発。

課題 II:電子機器の外部から観測される情報を用いて不正動作を検知する技術

(ア)組み込みマイコンやFPGA等のチップに不正回路が含まれることを想定し、その動作をモデル化。当該モデルに基づき、電子機器の外部から観測される情報より、不正動作と正常動作を識別するために有意となる特徴量を抽出する技術の研究開発。

(イ)AIを活用し不正動作の特徴量と正常動作の特徴量を学習することにより、電子機器の外部から観測される情報の中から不正動作の位置を検知する技術の研究開発。

ラックはこのうち、課題 II(イ)の「AI/機械学習に基づく不正動作検知技術に関する研究開発」を担当する。

関連記事

この記事の写真

/